If ( reset = 1 ) begin //active high resetĬ = cin //on first iteration after reset, assign cin to c.įlag = 1 //then make flag 1, so that this if statement isnt executed any more.Ĭ = ( a & b ) | ( c & b ) | ( a & c ) //CARRY Output reg s, cout //note that s comes out at every clock cycle and cout is valid only for last clock cycle. Input a, b, cin, //note that cin is used for only first iteration. Note that we dont have to mention N here. Though I have used behavioral level approach to write my code, it should be straight forward to understand if you have the basics right.

In this post, I have used a similar idea to implement the serial adder.

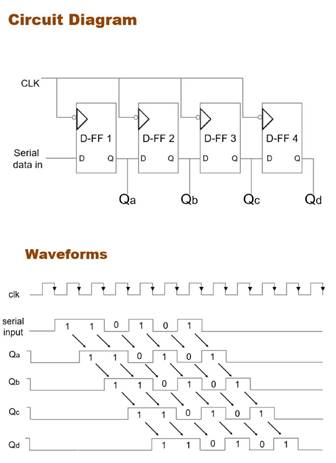

The D flipflop is used to pass the output carry, back to the full adder with a clock cycle delay. The above block diagram shows how a serial adder can be implemented.

0 kommentar(er)

0 kommentar(er)